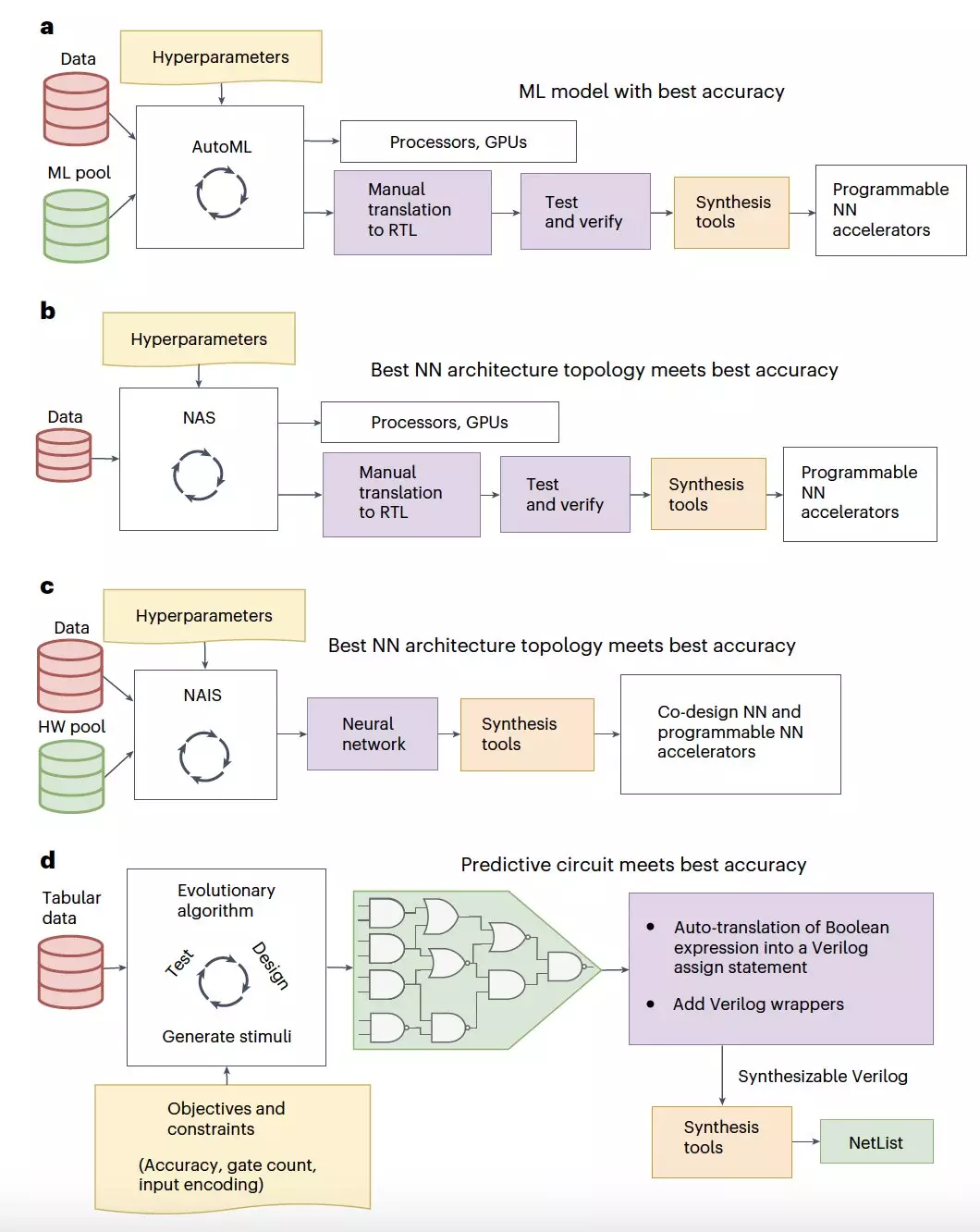

The advancement of deep learning techniques has revolutionized various fields such as image classification and natural language processing. With the rising demand for more efficient computational solutions, researchers have been exploring the development of hardware accelerators specifically designed to run deep neural networks. Recently, a team of researchers from the University of Manchester and Pragmatic Semiconductor introduced a new approach to automatically generate classification circuits, known as “tiny classifiers,” from tabular data.

The methodology proposed by Iordanou, Atkinson, and their team involves the use of tiny classifier circuits composed of only a few hundred logic gates. Despite their compact size, these circuits have proven to deliver accuracy levels comparable to state-of-the-art machine learning classifiers. By utilizing an evolutionary algorithm to search through the logic gate space, the researchers were able to optimize training prediction accuracy while limiting the number of logic gates to 300 or fewer.

Through a series of simulations, the researchers demonstrated the effectiveness of their tiny classifiers in terms of accuracy and power consumption. The results showed significant improvements over traditional machine learning baselines, with the tiny classifiers using substantially less area and power. Additionally, the researchers validated their approach by implementing the tiny classifiers on a low-cost integrated circuit, further showcasing their efficiency and performance benefits.

The development of tiny classifiers holds great potential for a wide range of real-world applications. These circuits could be utilized as triggering mechanisms on chips for smart packaging and monitoring of various products. Additionally, they could contribute to the development of low-cost near-sensor computing systems, enabling efficient processing of data in resource-constrained environments.

The research conducted by the team at the University of Manchester and Pragmatic Semiconductor represents a significant advancement in the field of deep learning accelerators. The implementation of tiny classifiers as a novel approach to generating classification circuits has yielded promising results in terms of accuracy, efficiency, and power consumption. As the demand for more powerful and resource-efficient computing solutions continues to grow, the development of such innovative hardware accelerators is essential for driving the evolution of artificial intelligence and machine learning technologies.